数字闹钟作为现代生活中不可或缺的计时工具,其核心在于精确、稳定的计时电路设计。采用3817集成电路设计的数字闹钟,以其集成度高、功能完善、可靠性强等特点,成为一种经典且实用的设计方案。本文将围绕3817集成电路的核心特性,详细解析其构成的数字闹钟电路的工作原理与设计要点。

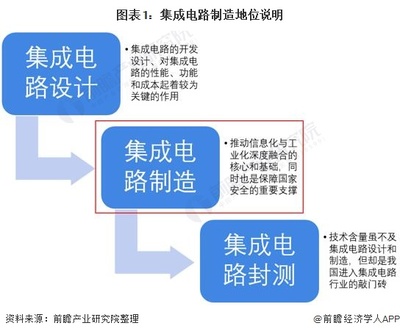

一、3817集成电路概述

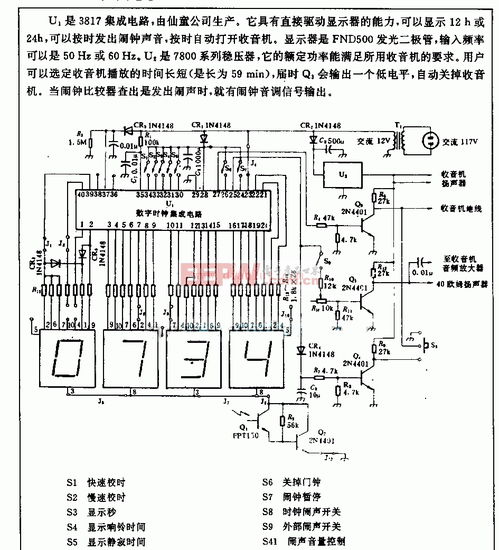

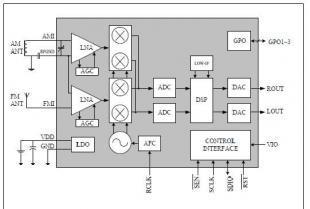

3817是一款专用的数字闹钟集成电路芯片,通常集成了计时、闹铃控制、显示驱动等核心功能模块。其内部通常包含:

1. 时基振荡电路:通常外接石英晶体(如32.768kHz),产生高精度的时间基准信号。

2. 分频与计时逻辑:将振荡频率分频得到标准的秒脉冲,并据此进行秒、分、时的计数与进位。

3. 时间设置与闹铃设置逻辑:提供按键输入接口,用于调整当前时间和设定闹铃时间。

4. 显示驱动电路:直接输出驱动LED数码管或LCD显示屏的信号,如段码和位码。

5. 闹铃比较与输出控制:将当前时间与设定闹铃时间进行比较,在匹配时触发音频或蜂鸣器驱动电路。

二、电路系统构成

一个完整的基于3817的数字闹钟电路系统通常由以下几部分组成:

- 核心控制芯片:3817集成电路。

- 时基电路:由石英晶体和微调电容构成,为芯片提供稳定的时钟源。

- 显示单元:通常采用4-6位LED数码管(显示时分、分秒或时分秒),或专用的LCD屏。

- 输入单元:轻触按键或拨码开关,用于模式切换、时间/闹铃设置(加、减)。

- 闹铃输出单元:三极管驱动的小型蜂鸣器或扬声器,播放提示音。

- 电源电路:提供稳定的直流低压(如3V或5V)电源,可能包含备用电池接口,在主电源断电时维持计时。

三、工作原理与流程

- 计时:石英晶体振荡电路产生高频脉冲,经芯片内部分频器分频后得到精确的1Hz秒信号。该信号驱动内部的计时计数器,完成秒、分、时的累计与显示更新。

- 时间设置:用户通过“模式”键进入设置状态,再通过“加”、“减”键对闪烁显示的时、分、秒等位进行校正。设置完成后,芯片恢复正常的计时模式。

- 闹铃功能:用户通过类似流程设定闹铃的时和分。芯片内部不断将当前时间与设定闹铃时间进行比较。当两者完全匹配时,闹铃控制逻辑被触发,驱动输出引脚产生一定频率的脉冲信号(或持续信号),经三极管放大后推动蜂鸣器发声。通常设有“止闹”按键来手动关闭铃声。

- 显示驱动:芯片的段码输出(a, b, c, d, e, f, g, dp)直接或通过限流电阻连接到所有数码管的对应段。位码输出(COM1, COM2, ...)则通过晶体管扫描驱动各个数码管的公共极,利用人眼视觉暂留效应实现多位数字的动态稳定显示。

四、设计要点与优势

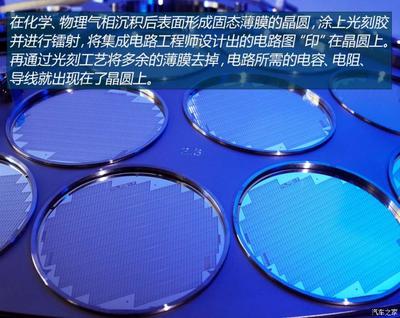

- 集成化设计:3817将大部分逻辑功能集成于单一芯片,极大简化了外围电路,提高了系统的可靠性与一致性,降低了生产成本。

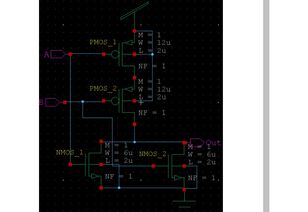

- 低功耗:采用CMOS工艺,静态功耗极低,特别适合采用电池供电或需要备用电池的场合。

- 抗干扰性:内部数字逻辑电路具有较好的抗干扰能力,配合稳定的晶振,能保证长时间精确运行。

- 设计灵活性:虽然芯片功能固定,但开发者仍可通过外围电路扩展功能,如增加亮度调节、多种闹铃音、贪睡功能(Snooze)等。

五、

采用3817集成电路设计数字闹钟,是一种成熟、高效的工程方案。它平衡了性能、成本与复杂度,使得设计者能够快速构建出功能稳定、显示清晰、操作简便的数字计时产品。理解其内部结构和工作原理,不仅有助于此类产品的开发与维护,也为学习数字逻辑电路与微电子应用提供了良好的实践范例。随着技术进步,虽然更智能的MCU方案日益普及,但这种专用集成电路的设计思想及其体现的系统集成理念,在电子产品设计中依然具有重要的参考价值。