混合信号集成电路是指在同一芯片上同时集成了模拟电路和数字电路的集成电路。其设计流程融合了模拟与数字设计的特点,技术复杂且要求严格,通常遵循一个系统化、层次化的过程。以下是其基本设计流程的详细解析。

一、 系统定义与规范制定

设计流程始于市场或系统需求分析。设计团队需要明确芯片的功能、性能指标(如模拟部分的精度、带宽、信噪比;数字部分的处理速度、逻辑资源)、功耗预算、工作电压、温度范围、封装形式以及成本目标。此阶段输出一份详细的系统规范文档,作为后续所有设计活动的准绳。

二、 架构设计与模块划分

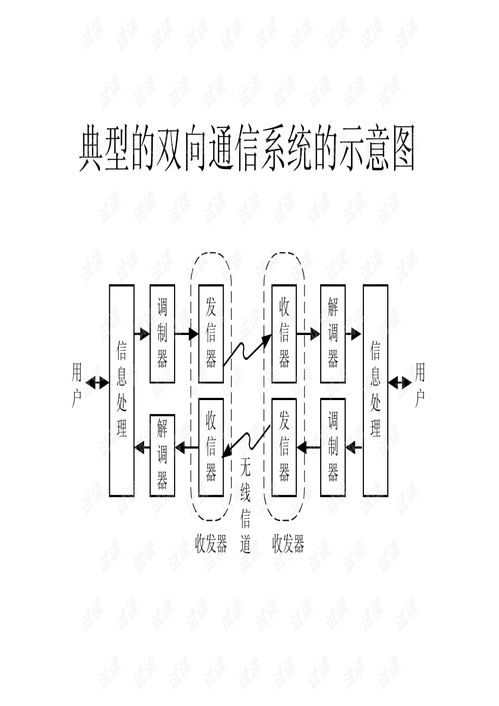

根据系统规范,进行顶层架构设计。核心任务是将复杂系统分解为若干个功能模块,例如:模拟前端(放大器、滤波器、模数转换器ADC)、数字信号处理核心、数据接口、时钟管理、电源管理等。必须精心规划模拟与数字模块之间的接口(如数字控制信号对模拟模块的干扰,模拟信号向数字域转换的同步问题)以及电源和地线的布局策略,以最大限度地减少串扰。

三、 电路设计与仿真

此阶段是设计的核心,通常模拟与数字部分并行开展,但需保持紧密协调。

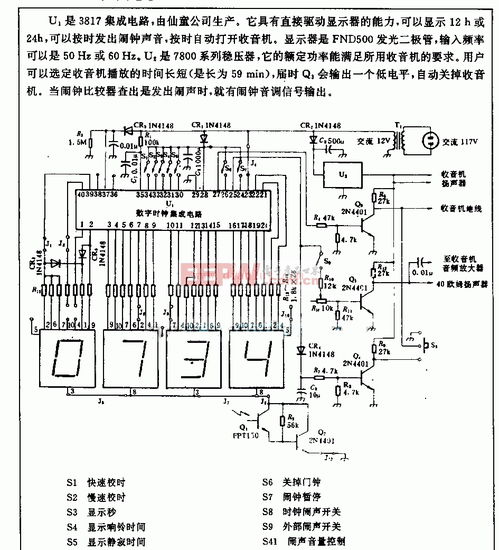

- 模拟电路设计:设计者使用晶体管级电路图输入工具,设计运算放大器、比较器、基准电压源、锁相环(PLL)等模拟模块。每个模块都需要进行深入的直流、交流、瞬态及噪声仿真,以确保其性能(增益、带宽、线性度、功耗等)满足规范。

- 数字电路设计:通常采用硬件描述语言(如Verilog或VHDL)进行寄存器传输级(RTL)描述,定义数字模块的功能和时序。然后通过逻辑综合工具,将RTL代码映射到目标工艺库的标准逻辑单元,生成门级网表。随后进行静态时序分析,确保建立时间和保持时间满足要求。

四、 混合信号仿真与验证

这是混合信号设计特有的关键环节。将模拟模块的晶体管级网表(或行为级模型)与数字模块的门级网表一同放入混合信号仿真器(如AMS仿真器)中进行协同仿真。目的是验证数字控制逻辑能否正确驱动模拟模块,评估模拟-数字接口(如ADC/DAC)的整体性能,以及至关重要的——分析数字开关噪声通过衬底和电源线对敏感模拟电路的影响(即衬底噪声和电源噪声耦合)。

五、 版图设计

版图是将电路图转换为一系列几何图形,这些图形定义了芯片制造所需的各层掩膜。混合信号版图设计极具挑战性,需遵循诸多特殊规则:

- 隔离与保护:对敏感模拟模块(如高增益放大器、基准源)采用保护环、隔离阱、单独供电引脚等措施,以屏蔽数字噪声。

- 匹配设计:对于差分对、电流镜等对匹配度要求高的元件,需采用共质心、交叉耦合等版图技术来降低工艺偏差影响。

- 信号走线:模拟信号线应尽量短,并可能采用屏蔽线;数字信号总线需注意串扰。

- 电源与地线:通常为模拟和数字部分提供独立的电源和地线引脚,并在版图内部分开布线,最后在封装引脚处单点连接,形成“星型”接地,以避免噪声环路。

六、 版图后仿真与物理验证

完成版图后,必须提取版图的实际寄生参数(寄生电阻、电容,乃至电感),将这些参数反标回电路网表,进行带寄生参数的仿真。这一步至关重要,因为寄生效应会显著劣化电路性能(尤其是高频模拟电路)。只有后仿真结果满足规范,设计才能进入下一阶段。必须进行设计规则检查(DRC)以确保符合晶圆厂工艺要求,以及进行版图与电路图一致性检查(LVS)。

七、 流片与测试

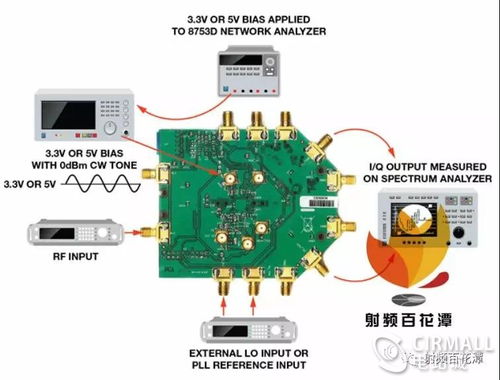

所有验证通过后,将版图数据(GDSII格式)提交给晶圆代工厂进行制造,此过程称为“流片”。芯片制造完成后,需要进行严格的测试。测试分为晶圆测试和封装后测试,使用自动测试设备(ATE)和定制测试板,验证芯片的所有直流、交流、功能及动态性能是否与设计目标一致。

混合信号集成电路设计是一个反复迭代、不断验证的复杂工程过程。模拟与数字设计的深度融合、对噪声和寄生效应的严格控制贯穿始终。随着工艺节点的不断进步,设计挑战日益增大,因此严谨的流程、先进的设计工具以及丰富的经验是成功设计混合信号芯片的关键。