在当今数字化时代,芯片作为电子设备的核心,其内部集成了数十亿甚至上百亿个晶体管,却能被封装在指甲盖大小的空间中。这令人惊叹的微小化背后,是长达半个多世纪的集成电路设计与制造技术的持续精进,尤其离不开被誉为‘芯片之母’的光刻技术。本文将深入解析芯片如何从设计到制造,一步步打造出无比精密的‘电路城市’。

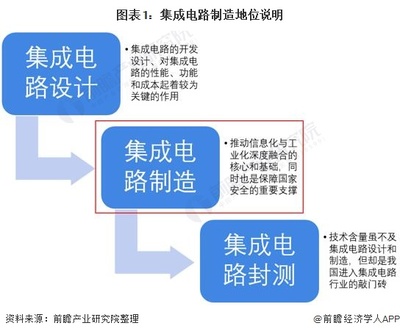

一、集成电路设计:绘制微观城市的蓝图

芯片的微小化首先源于精妙的设计。集成电路设计如同城市规划,工程师们利用电子设计自动化(EDA)工具,在虚拟空间中绘制出复杂的电路图。通过逻辑设计、电路设计和物理设计等步骤,将数十亿个晶体管、电阻、电容等元件及其连接线,以极高的密度和最优的布局‘安置’在芯片上。设计过程中的每一层都力求最小化面积、降低功耗并提升性能,为后续的制造奠定了微观基础。

二、光刻技术:雕刻微观城市的核心工艺

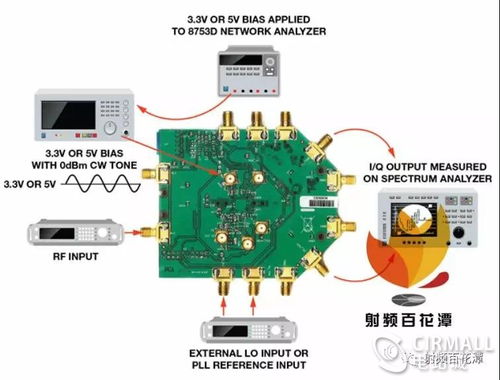

光刻是芯片制造中最关键、最复杂的步骤,它决定了芯片能有多小。其原理类似于照相技术,但精度达到了纳米级别。光刻机将设计好的电路图案通过光学系统投射到涂有光刻胶的硅片上,利用光化学反应将图案‘刻印’上去。

- 光学系统与波长:光刻的精度很大程度上取决于所用光源的波长。根据瑞利判据,分辨率与波长成正比,波长越短,能刻出的线条就越细。从早期的紫外光(UV)到深紫外光(DUV,如193nm ArF激光),再到极紫外光(EUV,波长13.5nm),波长的缩短使得晶体管尺寸从微米级缩小到如今的纳米级(如5nm、3nm工艺)。

- 光波与精进:EUV光刻是当前最前沿的技术。它使用极短的13.5nm波长光波,通过复杂的反射式光学系统(因为EUV会被几乎所有材料吸收),能够在硅片上刻出更精细的图案。EUV技术面临光源功率、光学元件精度等巨大挑战,其发展体现了人类在光学和材料科学上的巅峰成就。

三、制造工艺的协同精进:打造完整的电路城市

光刻并非孤立存在,它需要与蚀刻、离子注入、薄膜沉积等上百道工艺步骤紧密配合。例如,多重曝光技术利用多次光刻和蚀刻来创造比单一曝光更小的特征尺寸;而三维晶体管(如FinFET)结构则通过立体设计,在有限平面上进一步提升集成度。整个制造过程在超净环境中进行,确保‘城市’的每一‘建筑’都精准无误。

四、为什么能这么小?技术极限与未来展望

芯片的微小化是摩尔定律驱动下的持续创新结果。其根本原因在于:

- 物理原理的深度应用:利用更短波长光波突破衍射极限。

- 材料与工程的突破:新型光刻胶、高精度镜头和硅片处理技术。

- 设计工具的进化:EDA软件使复杂设计成为可能。

随着尺寸逼近物理极限(如量子隧穿效应),进一步缩小面临巨大挑战。芯片发展可能转向三维集成、新器件结构(如GAA晶体管)及新材料(如二维材料),继续推动这个微观‘电路城市’向更高效、更智能的方向演进。

芯片内部之所以能如此之小,是集成电路设计与光刻技术数十年精进的结晶。从光学波长的缩短到制造工艺的协同,人类正以非凡的智慧,在纳米尺度上构建着支撑现代文明的微观王国。