引言

在现代高速数据采集系统、医疗仪器、工业控制以及通信设备中,模数转换器(ADC)扮演着将模拟世界与数字世界连接起来的关键角色。AD7862是一款由ADI公司生产的高性能、双通道、12位、1MSPS采样率的逐次逼近型(SAR)ADC,以其优异的动态性能和低功耗而著称。为了充分发挥其性能,并实现灵活、可重构的数据采集前端,现场可编程门阵列(FPGA)成为实现其接口与控制逻辑的理想平台。本文将探讨基于FPGA的AD7862接口电路的设计原理、关键模块实现以及设计考量。

一、 系统架构与设计目标

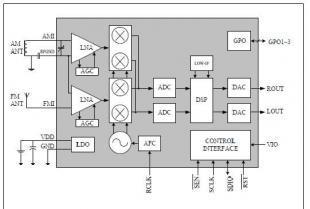

基于FPGA的AD7862接口电路系统通常由以下几个核心部分组成:

- 模拟前端调理电路:负责对输入模拟信号进行缓冲、缩放、滤波等处理,以满足AD7862的输入范围和要求。

- AD7862芯片及其外围电路:包括基准电压源、去耦电容、时钟网络等,确保ADC稳定工作。

- FPGA核心控制逻辑:这是设计的核心,负责产生AD7862所需的所有控制时序(如CONVST、CS、RD等),读取转换后的数据,并进行可能的预处理(如数据对齐、格式转换)。

- 数据输出接口:将采集到的数据通过FPGA内部总线(如Wishbone、AXI)或外部接口(如UART、SPI、以太网)传输至处理器或上位机。

设计目标主要包括:

- 时序精确性:严格满足AD7862数据手册中规定的建立/保持时间、脉冲宽度等时序参数。

- 高数据吞吐率:充分利用AD7862的1MSPS采样能力,设计高效的数据流控制。

- 灵活性与可配置性:利用FPGA的可编程性,实现采样率、通道选择(双通道顺序或同时采样模式)等参数的灵活配置。

- 稳定性和抗干扰能力:良好的PCB布局布线及电源完整性设计,确保数字噪声对模拟信号的干扰最小化。

二、 关键接口信号与FPGA逻辑设计

AD7862的主要控制信号包括:

- CONVST(转换启动):下降沿启动A/D转换过程。其频率直接决定了采样率。

- CS(片选)与 RD(读使能):用于从ADC输出寄存器中读取数据。通常需要配合使用。

- BUSY:输出信号,高电平表示转换正在进行,下降沿表示转换完成,数据已准备好。

- DB0-DB11:12位并行数据输出总线。

在FPGA内部,可以使用有限状态机(FSM)来精确控制整个“启动转换-等待完成-读取数据”的循环。一个典型的状态机可以设计为四个状态:

- IDLE:空闲状态。等待启动信号或内部定时器触发。

- START_CONV:拉低CONVST信号,启动一次转换,然后进入等待状态。

- WAIT_BUSY:监控BUSY信号,等待其从高变低(转换完成)。

- READ_DATA:在BUSY变低后,操作CS和RD信号,将数据总线上的值锁存到FPGA内部寄存器中。完成后返回IDLE状态,准备下一次转换。

对于双通道操作,需要根据AD7862的模式选择引脚(MODE)进行配置,并在状态机中增加通道选择与控制逻辑。

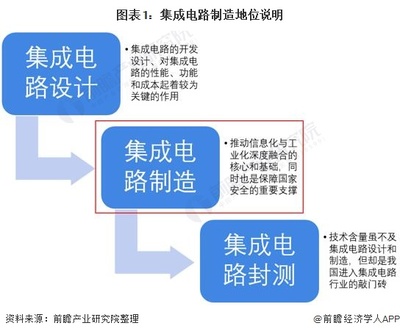

三、 集成电路设计考量

虽然FPGA实现了数字接口逻辑,但整个系统作为一块集成电路板,其设计质量至关重要:

- 电源与地设计:AD7862要求高品质的模拟电源(+5V AVDD)和数字电源(+5V DVDD)。必须使用磁珠或电感进行隔离,并布设充足的去耦电容(通常为0.1μF陶瓷电容靠近电源引脚,并辅以10μF钽电容)。模拟地和数字地应在芯片下方单点连接。

- 基准电压源:AD7862内置2.5V基准,也可使用外部更高精度的基准(如ADR421)。基准引脚必须用低ESR电容充分去耦。

- 信号完整性:

- 模拟输入路径:应尽量短,并采用屏蔽或用地线包围,远离高速数字信号线。串联小电阻有助于减少反射。

- 数字信号线(特别是CONVST和时钟):应视为传输线,必要时进行端接匹配,以减少振铃和过冲,确保时序边缘清晰。

- 数据总线:走线应等长,以减少数据偏移(skew),保证FPGA能同时捕获所有位。

- 时钟管理:AD7862的转换时钟可由内部产生或外部提供。若使用外部时钟,需确保其干净、稳定。FPGA产生的CONVST信号也应有低抖动的时钟源驱动。

四、 FPGA内部的高级功能集成

利用FPGA的并行处理能力和丰富资源,可以在接口逻辑之上集成更多功能,提升系统集成度:

- 数据缓存:使用FPGA内部的Block RAM或FIFO,构建数据缓冲区,以匹配ADC高速输出与后续相对低速处理或传输之间的速率差异。

- 实时处理:可集成数字滤波器(如FIR、IIR)、平均值计算、峰值检测等预处理算法,减轻后端处理器的负担。

- 多芯片同步:对于需要多片AD7862同步采样的应用,FPGA可以产生全局同步的CONVST信号,实现精确的通道间同步。

- 自测试与校准逻辑:可以设计逻辑,周期性地向ADC输入已知的测试信号(或利用内部特性),监测其输出,实现系统的在线自检和软件校准。

五、 验证与测试

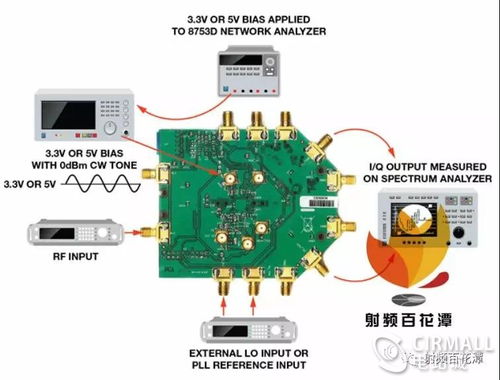

设计完成后,必须进行 rigorous 的验证:

- 功能仿真:使用ModelSim等工具,编写测试平台(Testbench),模拟AD7862的行为模型,验证FPGA状态机逻辑和时序的正确性。

- 时序分析:在FPGA综合布局布线后,进行静态时序分析(STA),确保所有路径满足建立和保持时间要求,特别是与ADC接口的关键路径。

- 板级测试:

- 使用示波器测量关键控制信号(CONVST, BUSY, RD)的时序关系,确保符合数据手册要求。

- 使用信号发生器输入标准正弦波,采集数据并分析其信噪比(SNR)、有效位数(ENOB)等动态性能指标,评估整个系统的实际性能。

结论

基于FPGA的AD7862接口电路设计,是一个融合了模拟电路设计、数字逻辑设计和高速PCB设计技术的综合性项目。通过精心设计FPGA内部的状态机控制逻辑,并严格遵守ADC的模拟和数字接口要求进行板级集成电路设计,可以构建一个高性能、灵活可靠的数据采集系统。FPGA的可编程特性为进一步的系统功能集成和优化提供了无限可能,使得该方案在众多高要求的工业与科研领域具有广泛的应用前景。