在集成电路(IC)设计与验证流程中,Calibre是业界广泛使用的物理验证工具。设计工程师,尤其是在后端设计阶段,常会遇到各种报错,其中“Extra Pins”(多余引脚)报错是一个典型问题。本文将简要分析此报错,并汇总包括EETOP、创芯网等在内的主流半导体技术论坛,为工程师提供问题排查与交流的平台参考。

一、Calibre “Extra Pins” 报错浅析

“Extra Pins”报错通常发生在进行布局与布线(LVS)验证时。其核心含义是:在提取出的版图(Layout)网表中,存在某些电气节点(即“引脚”),这些节点在对应的参考原理图(Schematic)网表中并不存在。

可能的原因及排查思路:

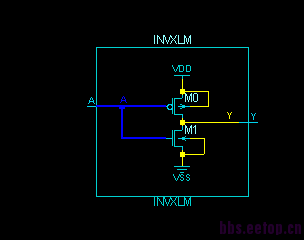

1. 版图绘制错误:最常见的原因。例如,在绘制版图时,不小心多放置了未连接的金属线、接触孔或通孔,Calibre在提取时将其识别为一个独立的电气节点,从而被视为“多余引脚”。

2. 器件层次或属性错误:某些器件的版图形状(如Guard Ring、Dummy Device)如果处理不当,可能被提取出额外的端口。

3. 电源/地网络处理:如果版图中的电源(VDD)、地(VSS)网络名称或连接方式与原理图不完全一致,也可能引发此类报错。

4. 文本层(Text Layer)误标:错误的标签(Label)放置,可能误导提取工具识别出非预期的引脚。

解决步骤:

1. 仔细查看Calibre报错报告,定位到具体的版图坐标和网络名称。

2. 在版图编辑工具(如Virtuoso)中跳转到对应坐标,检查该区域的图形和连接。

3. 确认该节点是否确实为冗余图形,若是则删除;若非冗余,则需检查其是否应与原理图中的某个现有节点相连,或者原理图是否需要相应修改。

二、后端设计与半导体技术交流论坛推荐

遇到复杂问题,自学排查往往效率有限。积极参与专业的技术社区讨论,是工程师快速成长和解决问题的有效途径。以下是一些在微电子、集成电路设计领域极具影响力的中文论坛:

- EETOP 创芯网论坛

- 定位:国内最知名、最活跃的集成电路与电子工程综合社区之一。

- 优势:

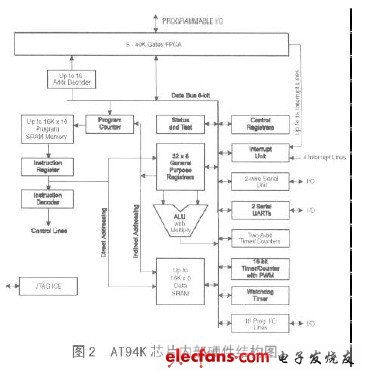

- 板块全面:涵盖数字前端/后端设计、模拟/RF IC设计、FPGA、嵌入式系统、半导体制造、EDA工具使用等多个子板块。

- 资源丰富:拥有海量的学习资料、工具资源、技术文档和面经分享。

- 用户活跃:大量业内工程师、研究人员和学生聚集,Calibre等EDA工具的使用问题经常在此讨论,很容易找到相关帖子和解决方案。

- 创芯网论坛(原“中国半导体论坛”)

- 定位:专注于半导体行业的技术与资讯交流平台。

- 优势:在产业新闻、工艺技术、芯片设计方面有深度讨论,是了解行业动态和进行专业技术交流的好去处。

- 后端讨论区(通常指各大论坛的子版块)

- 在上述综合论坛中,“数字后端设计”、“版图设计” 等板块是专门讨论物理实现、静态时序分析(STA)、形式验证、物理验证(如Calibre、PVS)等后端核心议题的集中地。在这里提问“Extra Pins”等具体问题,更容易得到后端同行针对性的解答。

三、给工程师的建议

- 善用搜索:在提问前,先在论坛内使用“Calibre Extra Pins”、“LVS 多余引脚”等关键词搜索,很多常见问题已有详细解答。

- 规范描述:发帖提问时,应清晰描述问题、所用工艺节点、EDA工具版本,并附上关键的报错日志和截图(注意脱敏),这能极大提高获得有效帮助的概率。

- 跨界学习:集成电路设计是一个系统工程。后端工程师了解一些电路原理(前端),嵌入式工程师了解一些硬件特性(IC),都能拓宽解决问题的思路。这些论坛正是进行跨界知识补充的优质平台。

面对Calibre等EDA工具报错,系统性的自查与借助专业社区的力量相结合,是高效解决问题的关键。活跃于EETOP等工程师社区,不仅能解决眼前难题,更能持续跟踪技术动态,与业界同行共同进步。